Defense Ethernet Controller IP

Client Requirement

One of our North American Clients approached us with their requirements of designing a 100Mbps Ethernet controller to transmit the data from their high-security module over a high skew and noise lines. The challenge here is to design Ethernet PHY which can work with high noise and high skew signals.

Our Work

Sionsemi has suggested various encoders and decoders to reliably transmit over an ethernet network. The client has chosen the one that is best fit for their requirements, and architected, coded, verified and tested such Ethernet encoder and decoder along with its associated robust PHY that works for a wide range of noise and skew over an ethernet network.

Hardware Design

HW System architecture, design, test and bring up, including:

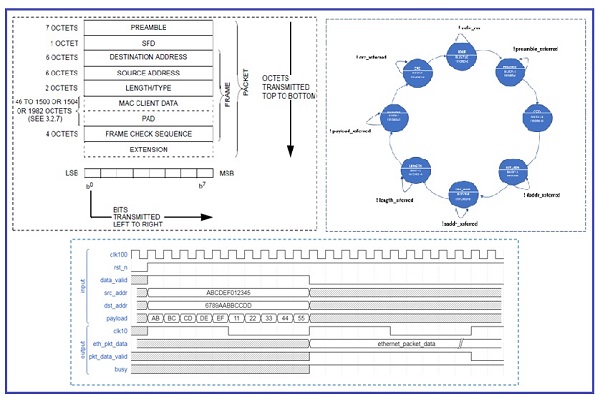

- Design architecture of IEEE 802.3 Ethernet controller

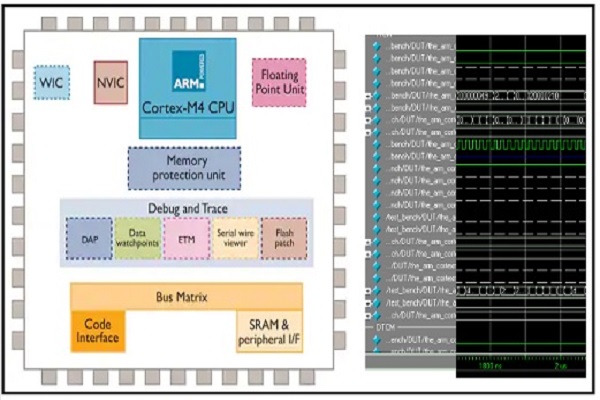

- Design architecture of 100Mbps Ethernet PHY

- Design architecture of Ethernet frame generator for HW testing

- RTL Coding

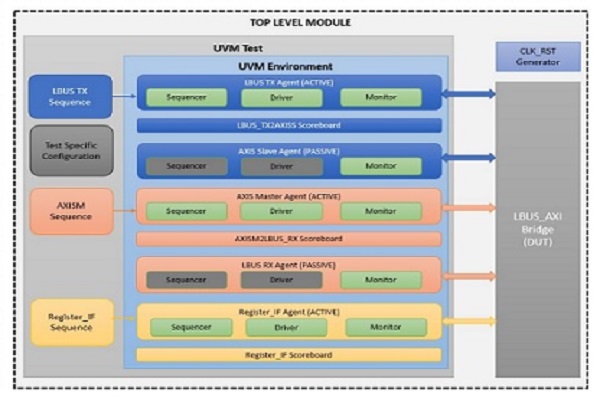

- Functional verification

- FPGA Implementation and bring-up

Technology Used

- IEEE 802.3 Ethernet Controller

- Ethernet PHY

- Ethernet traffic generator

- Verilog and SystemVerilog HDL