High Speed (560G) Ethernet IP Subsystem Integration & Design for a SOC

Client Requirement

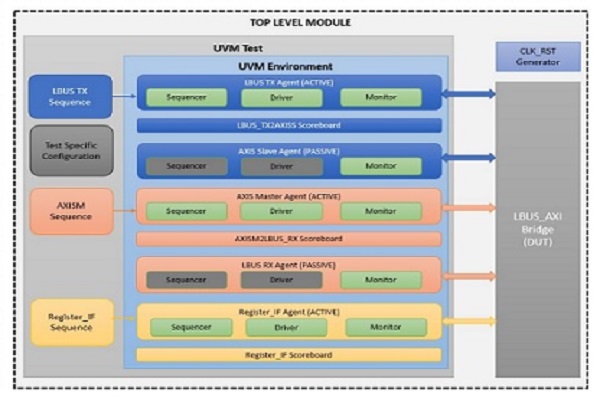

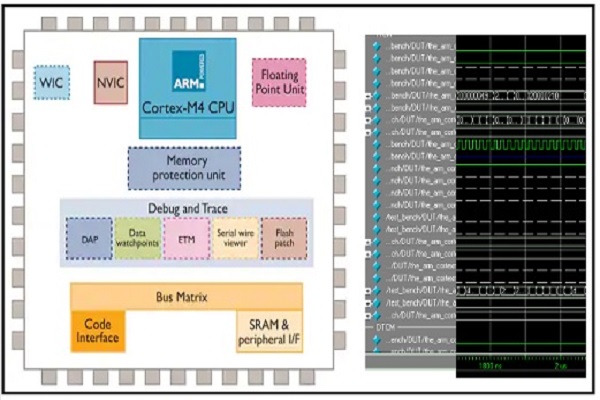

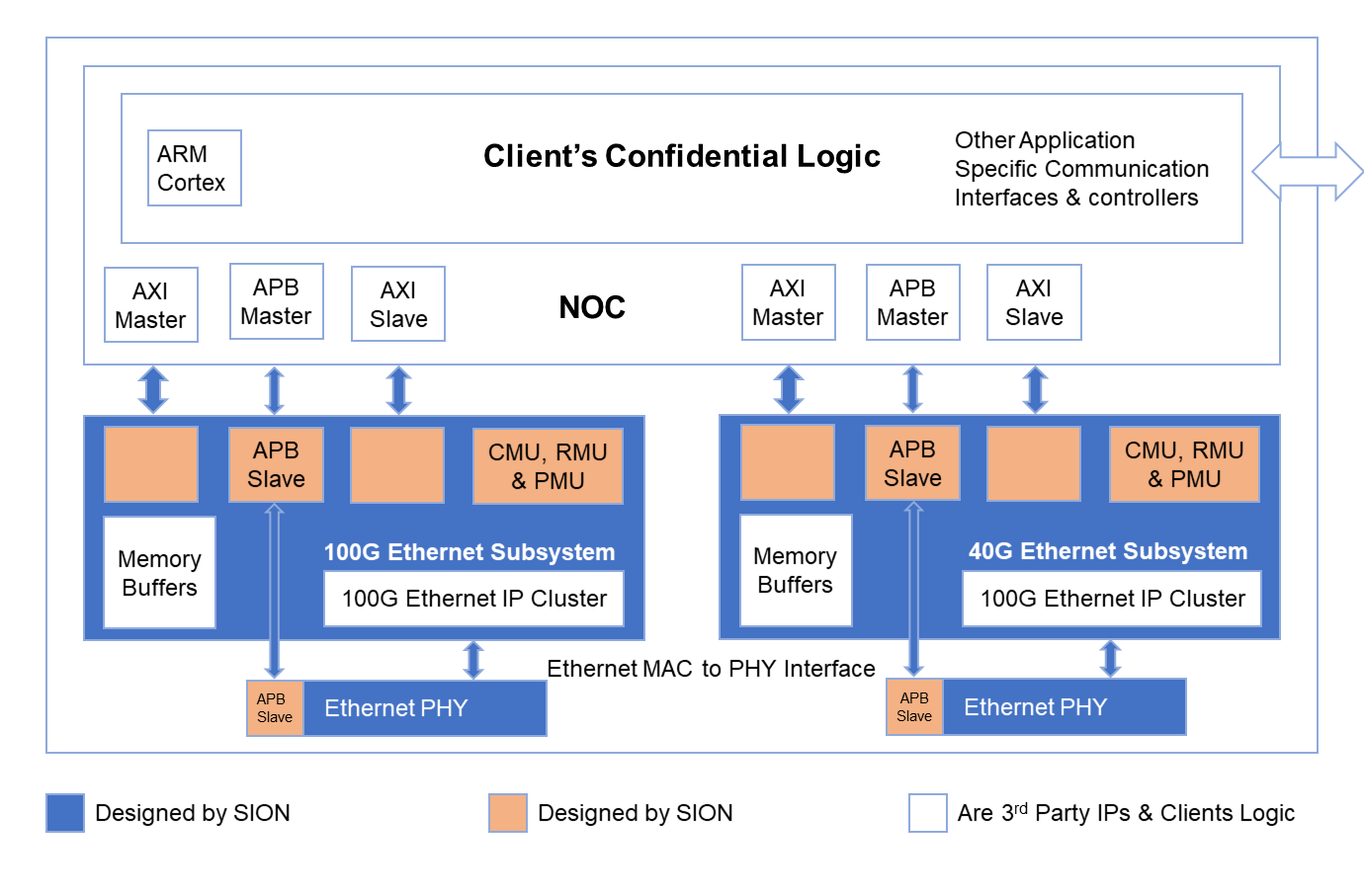

SION DV team handled successfully the project for one of our major clients requirement to design an ARM-based accelerator SoC consists of Ethernet subsystem which includes 2 subsystems such as 4- Lane 100G & 4 –Lane 40G Ethernet IP cores, both to be integrated to respective subsystems with Ethernet PHY & providing communication with NOC by AXI 4.0 Master-slave Interface. And providing access for CPU to configure IP subsystem registers through APB 3.0, to control various modes of operations.

Our Work

Hardware Design

- Integration of 3rd party 4 lane Ethernet 100G and 40G IPs onto client Subsytem

- Design and integration of AXI 4.0 master and slaves to interface Ethernet IP

- Design and integration of Clock, Reset and Power management blocks

- Design and integration of APB 3.0 register interface

- Timing closure of blocks at 1GHz

- Lint and CDC cleanup

- Verification support for Ethernet VIP integration and legacy testcases bring up

- DFT and MBIST cleanup

- Support for verification coverage closure

Technology Used

- 100G Ethernet & 40G Ethernet

- IEEE 802.3

- AXI 4.0

- APB 3.0

- 7nm technology node