PCIe Gen5 IP Subsystem Integration & Design for an SOC

Client Requirement

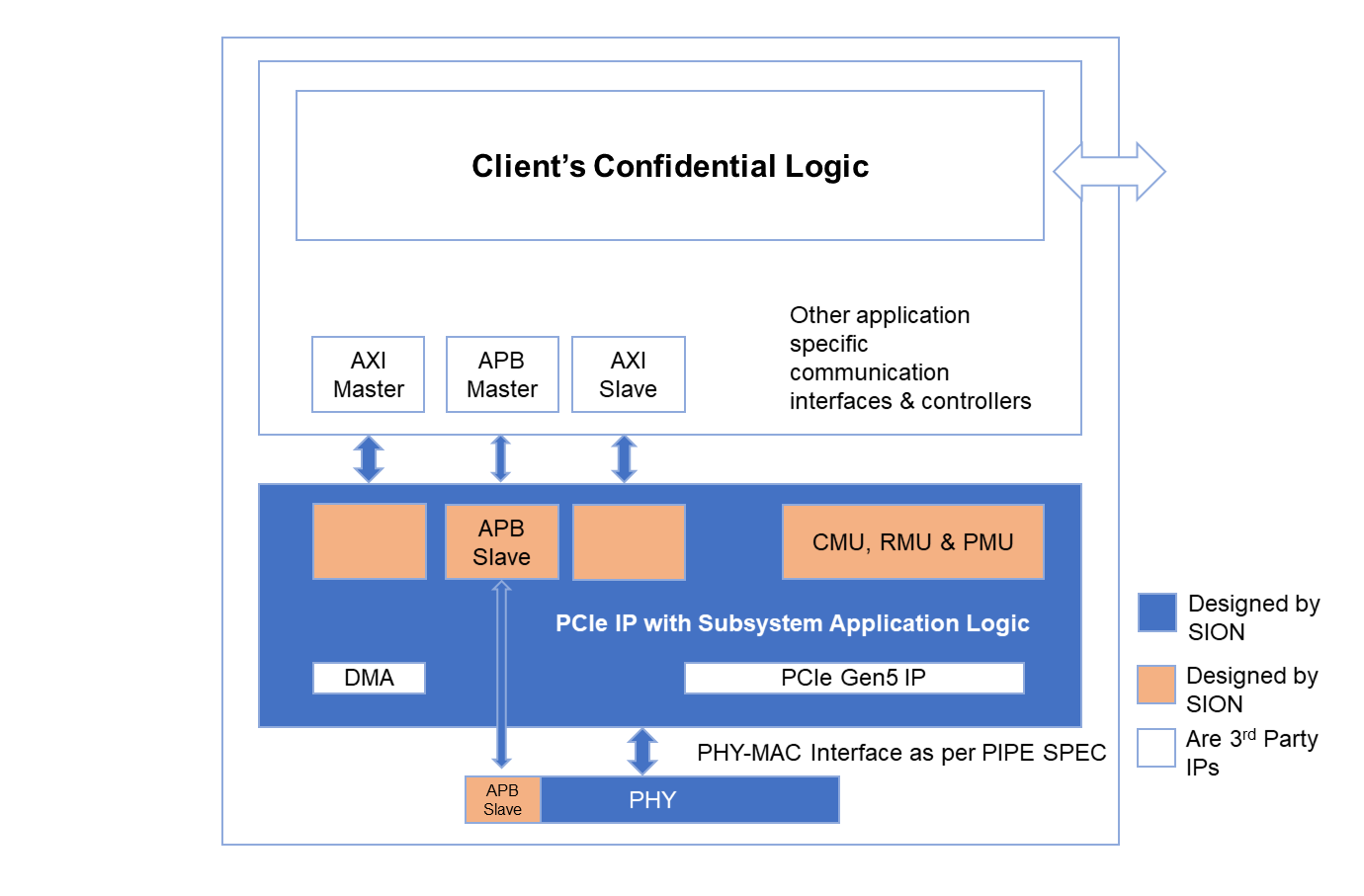

The client has approached us with their requirement of SoC consists of subsystem which includes PCIe IP core to be integrated with PHY (clients Specific SERDES complaint to PIPE Spec 5.2), DMA Engine, For IP – CPU connectivity & communication for NOC is with AXI 4.0 Master-slave Interface, And providing access for CPU to configure subsystem registers through APB 3.0. This work has been successfully handled by SIONSemi and delivered to the client within the expected time.

Our Work

Hardware Design

- Integration of 3rd party PCIe Gen5 IP onto client Subsystem

- Design and integration of PIPE interface as per PIPE v5.2

- Design and integration of Clock, Reset and Power management blocks

- Design and integration of APB 3.0 register interface

- Timing closure of blocks at 1GHz

- Lint and CDC cleanup

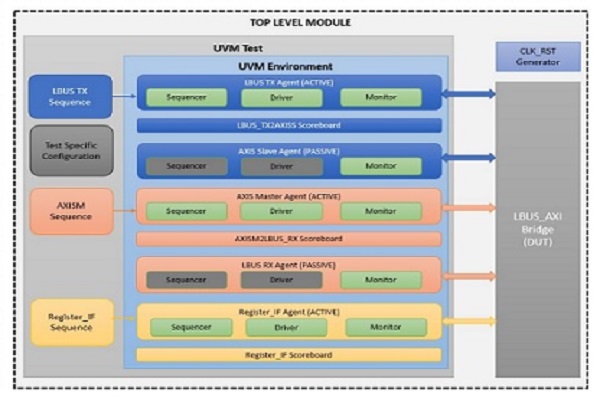

- Verification support for PCIe Gen5 VIP integration and legacy testcases bring up

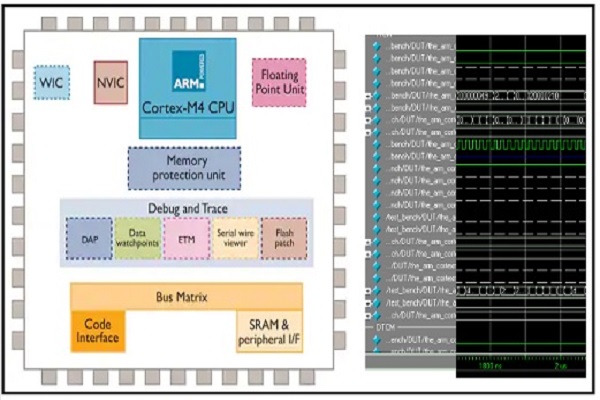

- DFT and MBIST cleanup

- Support for verification coverage closure

Technology Used

- PCIe Gen5

- AXI4.0

- APB3.0

- PIPE SPEC

- JTAG

- 7nm technology node