Physical Design Services

Our Physical Design team experienced in PD sign-off for various technology nodes such as 45nm, 28nm, 16nm, 7nm with designs levels like Full-chip/ SoC/ Subsystem/ IP/ Block level, SION Provides services from RTL/Netlist to GDSII flow ensure an aggressive schedule to launch without sacrificing QOR.

Our PD team expertise in:

- Full-Chip/System/SoC/IP/Cluster/Subsystem/Block level Synthesis

- DFT Insertion MBIST, BIST, ATPG, Scan and Fault Simulations

- I/O Planning/Floor-Planning/Power Planning/P&R/Metal Fills

- Design Partitioning And Hardening

- Abstract view generation and pinning

- Optimization of Area by estimation of Macros/IOs available logic

- Timing Budgeting and closure

- CTS and Analysis

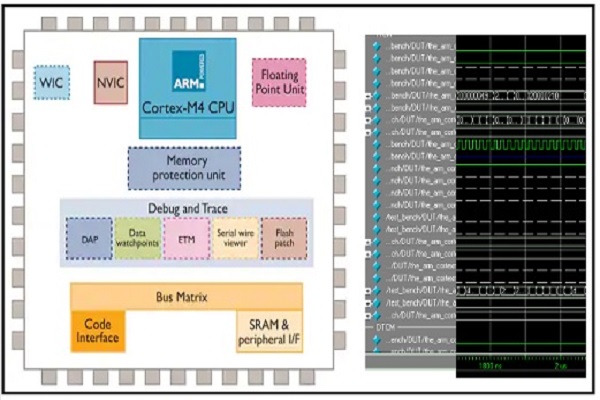

- Full-Chip level Integration of ARM Cores, IP’s, Subsystem, Hard-Macros

- Semi-Custom / Full Custom Implementations

- Full-Chip level Physical Verification DRC/ LVS/ Antenna /DFM checks

- Cross talk analysis

- Formal equivalence checks

- Low power implementations UPF / CPF flow development

Our PD Team comprises of:

- DFT team provides services for:

- SCAN Insertion

- Logic BIST

- Memory BIST

- ATPG

- Fault Simulations

- Implementation Team:

- Synthesis Flow

- Constraints & Exceptions

- Optimization techniques for timing and power

- Analysis & Debug skills for complex issues

- LEC

- Timing Analysis for Multi-Mode Multi-Corner

- I/O Planning &Partitioning

- Top Level Floor-Planning & Integration

- Block Level P & R

- Clock tree Building

- ECO Fixes & Signal integrity Analysis

- STA Sign-Off, Timing Closure

- PV Sign-Off flow setup & Execution

- IR Drop Analysis

- Supporting SI & Package team

- Tape-Out

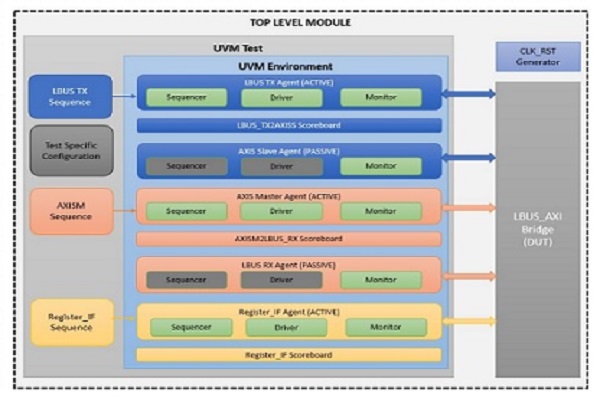

Our Verification Engineers Having experience in verifying:

- High-Speed protocol Interfaces with VIPs

- PCIe Gen1,2,3,4,5 With PIPE / SERDES

- Ethernet 100G, 40G, 10G, 1G

- USB 3.0, USB 2.0 host and device controllers

- AXI, AHB

- Other Interfaces like APB / SPI / UART /I2C

- DDR Controllers

- ARM SoC-based verification

- Audio Video Wireless protocols

- Formal verification

- Creating verification environment using UVM / OVM / VMM / SystemC /Specman / Vera

- Constrained Random Verification using golden reference models

- Modeling of analog and mixed-signal blocks using Verilog-AMS

- Porting the existing environment and verifying the use-case

- Verification closure including corner cases

- Coverage closure by using directed and randomized test cases

- Regression closure and automation handling in a platform like Jenkins