SoC Verification Services

Our Verification team experienced in various products at SOC / IP / Cluster / Subsystem / Block level, having experience in developing directed / Random test cases with strong debugging skills.

Our verification team expertise in:

- Full-Chip / System/SoC/IP/Cluster/Subsystem/Block level

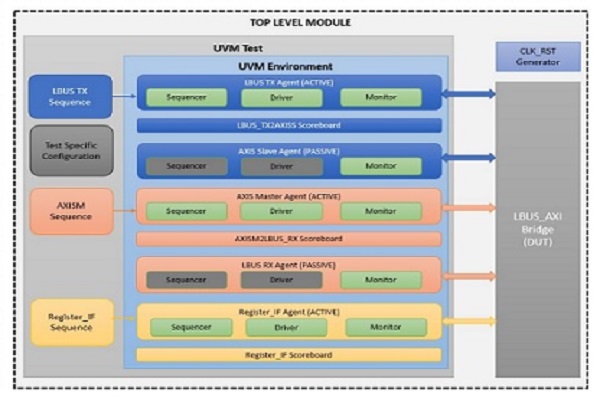

- Developing verification architecture from scratch with functional coverage & assertions

- VIP Development / Third party VIP’s Integration and verification

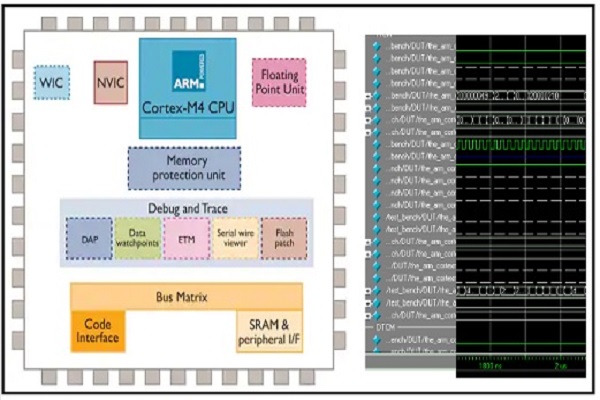

- ARM-Based CPU verification

- Hardware – Software CoSimulation

- Power-aware verification with UPF simulation

- Converting legacy test benches to SV / UVM

- Gate level Simulation / Pre & Post netlist SDF Simulation

Our Verification Engineers Having experience in verifying:

- High-Speed protocol Interfaces with VIPs

- PCIe Gen1,2,3,4,5 With PIPE / SERDES

- Ethernet 100G, 40G, 10G, 1G

- USB 3.0, USB 2.0 host and device controllers

- AXI, AHB

- Other Interfaces like APB / SPI / UART /I2C

- DDR Controllers

- ARM SoC-based verification

- Audio Video Wireless protocols

- Formal verification

- Creating verification environment using UVM / OVM / VMM / SystemC /Specman / Vera

- Constrained Random Verification using golden reference models

- Modeling of analog and mixed-signal blocks using Verilog-AMS

- Porting the existing environment and verifying the use-case

- Verification closure including corner cases

- Coverage closure by using directed and randomized test cases

- Regression closure and automation handling in a platform like Jenkins